確保委外晶圓製造IP安全性 美國業者提出方案

上網時間 : 2006年09月12日

從事安全技術開發的美國Certicom公司日前推出一項基於硬體的矽智權(IP)保護方案,採用了該公司的橢圓曲線加密(ECC)技術和20,000閘的嵌入式核心。隨著商用與軍用產品開發者開始關注半導體安全性技術,該公司希望此舉將有助於其獲得早期進入該市場的優勢。

雖然晶片設計業者越來越積極投單給中國大陸的新興晶圓代工廠,但是對中國以往在IP保護上的不確定性仍持保留態度。對於該議題的關注則有助於加速‘虛擬插槽介面聯盟’(VSIA)等組織的努力,該組織目前正致力於更新其基於軟體的IP標準。

在軍事方面,美國國防部先進研究計劃署(DARPA)先前提出在矽晶安全領域進行“科學、設備或系統之革命性進步”的呼籲。該計劃部份是美國國防部在去年2月所發表的一項研究所推動。該研究報告指出,鑑於在海外晶圓廠進行製造的晶片日漸增加,建議美國政府應增加防範。

大量的投資

由於委外晶片製造商可能製造出更多超乎訂單數量的晶片,並銷售到水貨市場上;因此,Certicom公司的新款硬體方案便是希望能夠防範這類事情的發生。儘管Certicom和其他業者未能明確提出這種剽竊生產的實例,但是Certicom公司負責新產品管理的Brian Neill指出,許多公司高度關切潛在的欺詐行為,特別是在中國,因為當地晶圓代工廠的成本竟可比其他國家還低40%。

“這些公司不想尋求新的代工廠,因為它們高度關注IP的問題,”Neill說,“大部份的公司也不想承認他們認為自己的公司受到剽竊。”

Certicom的方法是採用基於ECC的密鑰,該密鑰可以讓設計者隨心所欲地停用任何部份。新的密鑰可以在製造過程中的每一階段中另行增加進來,而僅能在生產的最後階段才可完全啟動該密鑰部份,例如在晶片被裝配到電路板上時。

Certicom現有的KeyInject控制器和伺服器將可為圖形晶片設計一類的公司提供支援,為其電路板級產品產生並置放ECC密鑰。Certicom公司在今年初專為感測器與RFID網路所推出的一款IP核心版本也將具備該ECC密鑰功能。

目前的產品主要是針對那些委託晶圓代工廠或封測公司為其製造晶片的無晶圓公司。未來的更新版本將為用於系統級產品的中介軟體提供基於核心的安全性。

儘管Certicom未讓任何專家審查該技術,但當論及該產品時,一家大型無晶圓廠半導體製造商的資深技術主管表現出高度的興趣。

“我們一直耗費大量精力於確保矽IP安全的措施,但是它卻無助於增加產品的價值或加速產品上市時間,”一位不願透露姓名的人表示。“那不是我們想做的事情。所以,如果有任何可解決這個問題的新技術,我想很多人都會感興趣的。”

該晶片公司目前正在中國最大的代工廠之一量產其舊式晶片,並且也採用該公司自己的晶片和系統來進行生產。“我們相當關注水貨市場的問題,但我們還沒親身經歷過”他說。

截至目前為止,該公司已經採用了各種商業措施以確保安全。但一般都只針對長期的代工關係,而在合約中要求非競爭條款、對代工廠電腦系統加以詳細審查,以及要求代工廠高層主管為安全政策背書。

此外,該公司經常向製作光罩的第三方進行投片,使代工廠只能得到生產的文件,而沒有原始的GDSII設計資料庫。“就生產流程來看,這是一場夢魘,而且會影響我們的交貨時間,”該主管人員表示。“我們也在內部討論因應的措施,例如使得NAND快閃記憶體佈局看來像NOR模組,使得反向工程更加困難,或者將測試和晶圓探測抽離出來而由不同的公司來完成。”

其他廣泛使用的方法還包括由VSIA設置附加的軟硬IP模組標準。“我相信許與我們共同合作的公司中都是採用這些技術,”無晶圓半導體協會(FSA)全球研究副總裁Lisa Tafoya說。

VSIA目前正進行浮水印、加密與指紋識別IP模組標準制訂的早期階段。許多公司都致力於制訂和促進VSIA安全規格,包括Cadence、飛思卡爾、IBM、英特爾、Mentor Graphics、飛利浦、Sonics、意法半導體以及TSMC等。

另外,FSA一直積極地鼓勵在中國進行IP交換的最佳做法。該協會在6月時與中國的三家半導體相關組織簽訂了初步協定,成立了大中華區貿易中心半導體IP貿易中心。該新組織將在中國、香港、台灣等地推動最佳技術、法規和商業實例,以支援FSA已經在相關問題上所做的工作。

美國國防部並正在該領域採取行動,部份動機來自於國防部科學委員會特別工作小組對於高性能微晶片供應的建議。2005年2月公佈的該工作小組報告,是源於2003年10月副部長Paul Wolfowitz的備忘錄,該備忘錄要求政府建構‘可信任的IC策略’。

該報告詳述了基於半導體製造代工廠遷移的風險,特別是在亞洲,以及軍事電子設備中越來越大量採用現成商業晶片之處。

目前,美國政府為其唯一的製造合作夥伴-IBM所製造的感測晶片建立了一款‘可信任的代工廠’專案。美國政府現並正與另一家高階晶片製造商進行第二個代工廠合作夥伴關係,但也體認識到該專案只是針對安全問題的一個短期補救措施。

為了尋求長期的解決方案,Darpa在六月份提出了IC信任計劃。研究人員直到八月中旬才對Darpa所號召的‘科學、設備或系統的革命性進步’做出回應,並用以驗證在製造過程中,最終用於武器中的晶片並未受到損害。

該提案還指出,製造商在生產IC時必須考慮到保護IP和軍事機密等問題。最後,Darpa表示必須找到一些技巧,使得那些不受美國法律控制的IC和系統能夠不被反向工程所破解。。

但目前仍不清楚美國要為該提案花費多少錢,以及美國預期所支援的研究多快能取得成效。

Semiconductor Insights公司副總裁兼CTO Ed Keyes回應該提案指出,某些安全性的威脅看來似乎很牽強。他說,代工廠通常“被嚴密地控制著”。要在設計規格以外額外生產晶片,你必須克服所有的警報系統,而這從一開始就會失敗。“他指出像特洛伊木馬程式的可能入侵,武器晶片可被設計成在某些條件下失效,例如在戰鬥中。”“但是這仍然需要經驗非常老練的人,”Keyes說。

就反向工程而言,Keyes指出確保安全的最好方式是採用FPGA設計,因為它很難在未被燒斷的保險絲中檢測到燒斷的熔絲。“對於每項連接,你都有99個其他的可能,但相較於ASIC,你所面臨的是巨大的成本和性能障礙。”

Chipworks公司的資深技術分析師Dick James說,儘管如此,反向工程仍難以避免。“它將耗費所有的時間和金錢。”James補充說,一項設計中最脆弱的階段就在於其仍然處在軟體形式之時。“軟體很容易被駭客入侵”,他說。

Certicom的作法

Certicom公司主管指出,他們並不知道Darpa的提案。然而,他們的技術顯然與軍事上的努力密切相關。

其核心即取決於主晶片中的一個處理元件。它“僅僅包含了一個密鑰擴展模組和一個解密模組”, Certicom公司的硬體工程總監Dan O'Loughlin說。

O'Loughlin說,該模組在製造過程中採用一次性可程式記憶體來儲存編程後的關鍵資料。它也需要光罩ROM,或其他類型的非揮發性記憶體來儲存加密指令。

解密指令則儲存於SRAM中,該SRAM是主晶片處理器中指令記憶體的一部份。該模組執行後續的電源重設,並且在主處理器的啟動程式碼中必須採用基本的客製韌體。

在電源重設時,最初的密鑰是由OTP中所讀取,而用於解密的密鑰則由密鑰擴展器產生並提供給解密模組。該解密模組從ROM中讀取加密指令,採用來自密鑰擴展器的密鑰並將密碼文字指令資料翻譯成純文字指令資料,再將解密指令寫入處理器的指令記憶體中。

接著,該韌體檢測到解密指令已經載入於指令記憶體,並跳轉到解密指令。而解密指令則可啟動晶片設計師所定義的特性。如果正確密鑰資料未出現的話,這些指令就會變為亂碼而避免所定義的特性生效。O'Loughlin說,晶片中未生效的部份仍可以透過傳統的BIST和自動掃描技術來測試。

Certicom正在開發另一種核心版本,可針對晶片的製程工作進行處理,例如未內建指令處理器的記憶體元件。還有一個版本可以驗證是否有人對晶片韌體進行過篡改。

該公司將對於產生密鑰的控制器以及在製造廠中將其載入晶片中的伺服器加以收費,該費用包含諮詢如何在設計中實現該核心。此外,Certicom也將根據其對於整個晶片價格的比重來收取專利費用。

用戶必須直接與其晶片製造夥伴共同合作來建置該方法。Certicom並未計劃直接向代工廠或封測廠進行銷售。

作者:麥利

測試服務相繼結束 WiMAX再掀新一輪部署浪潮

上網時間 : 2006年09月14日

WiMAX在許多地區的測試服務即將結束,結果顯示,此技術可望成為另一種真正可行的寬頻接取方式。在韓國的首都首爾,不斷擴建的‘WiBro’無線寬頻服務已經覆蓋了25%的區域。由此看來,英特爾公司近日向一家新創的WiMAX公司Clearwire投資6億美元的決定也就不足為奇了。

英特爾向該公司注入巨資的舉動,並使這家新創公司提升到與Sprint Nextel公司同樣的地位;Sprint Nextel是美國唯一一家近來對IEEE 802.16標準表現出極大興趣的傳統廠商。此外,摩托羅拉公司也對Clearwire進行了投資。

“這種大規模的高調投資可能會引發連鎖反應,例如使Sprint公司制訂更明確的計劃,或促使小型廠商在WiMAX部署方面做出一些具體決策。”ABI Research公司寬頻無線分析師Phil Solis指出。

就WiMAX的全球化發展來看,目前固定802.16d與行動802.16e標準都在英特爾統一力量之外尋找各自的獨立重心。而以投資來證明其重要性的一個關鍵就在於將WiMAX從目前的回程和都會區域網路基礎,轉變為一種能夠與全球網際網路及蜂巢式網路相互影響且普遍存在的寬頻服務。

迄今為止,現有802.16d固定WiMAX技術的載波主要被運用在兩個領域:蜂巢式回程服務,作為T1線或點對點光纖鏈路的替代方案;或者是與Wi-Fi網格聯合,在較大的都會區提供分層網格服務(tiered mesh services)。例如,摩托羅拉正積極籌備將其Canopy系統、網格網路及WiMAX相互結合,以提供‘分層無線寬頻’服務。

但是,WiMAX服務的實際行動將從為全國或區域性的消費者提供的WiMAX服務而展開。最新的802.16e(2005年的行動WiMAX標準)將較802.16d更容易被消費者所採納,原因不僅在於其具有行動性,還因為客戶設備的開發成本更為低廉。

如果那些樂觀的市場分析是正確的,那麼WiMAX的全球用戶數量將在2009年達到900萬(不包括蜂巢式回程基礎設備應用)。就某部份而言,這應可歸功於韓國對於WiBro這種早期的pre-WiMAX服務已相當熟悉,因此預估屆時將近半數的用戶將會集中於亞洲地區。

行動WiMAX之所以受歡迎部份得益於其建置時所具備的彈性。2006年2月發表的WiMAX服務大綱規定了5個頻段供選擇:2.3-2.4GHz、2.35-2.36GHz、2.496-2.69GHz、3.3-3.4 GHz, 以及3.4-3.8GHz。儘管大多數開發商都儘量避免802.16a中所規定的微波範圍,但是他們卻已經開始考慮5GHz及以上的其它頻段。

在這些頻帶中,開發商可以選擇1.25、5、7、8.75、10及20MHz的訊息通道頻寬。為了設計出較不複雜且低成本的收發器,大部份硬體建置都採用時分雙工(TDD)技術。但英特爾負責服務供應商產品的技術長Siavash Alamouti卻表示,為WiMAX選擇採用TDD技術是錯誤的。

“802.16e標準可採用頻分雙工(FDD)技術,而且考慮到頻譜分配或規格的要求,使用FDD似乎更有保障。”Alamouti認為。

英特爾新推出的Rosedale 2雙模基頻產品也許是最高規格的WiMAX基頻收發器晶片組。而像TI、飛思卡爾和Atmel等其它的基頻和RF專業廠商,例如都已與加拿大Wavesat公司合作開發用於客戶系統的mini-PCI參考設計。美國市場的其它晶片廠商還包括TeleCIS Wireless公司和富士通微電子(基頻/RF整合產品),以及Maxim公司、RF Magic、Sierra Monolithics和Theta等RF廠商。美國實力雄厚的OEM包括阿爾卡特/朗訊、Alvarion、Aperto、BelAir、Harris和摩托羅拉、北電以及許多新創企業等。

在美國的服務供應商中,早期的全國性WiMAX部署可以歸結為Clearwire和Sprint Nextel兩家公司之間的競爭。在Sprint併購Nextel之前,從用戶數量來看,兩者在2.5GHz頻段服務市場上各佔40%,儘管合併後的Sprint Nextel佔有80%的比例,但這並不代表其所覆蓋的區面積與用戶數一樣大。Clearwire公司則位居Sprint Nextel之後,是美國2.5GHz授權頻段的第二大企業。

自2003年成立以來,Clearwire公司的寬頻無線網路已經覆蓋了華盛頓州、俄勒岡州、愛達荷州、加州和內華達州的部份區域,並涵蓋德州、北卡羅萊納州、佛羅里達、威斯康辛與明尼蘇達州各地。Clearwire透過旗下的NextNet Wireless子公司,而在美國、墨西哥、加拿大和歐洲各地銷售基於OFDM的‘pre-802.16e行動WiMAX’系統。

Clearwire曾在今年七月獲得9億美元投資,其中包括英特爾投入了6億美元,這是該公司將其手機IC業務出售給Marvell所獲得的收入。另外的3億美元則來自於摩托羅拉投資部門Motorola Ventures。此外,摩托羅拉還同意收購NextNet,因而進一步開發NextNet的非視距(NLOS)設備,使其完全相容802.16e標準。

“英特爾在WiMAX領域已經採取了大量正確的措施,”Probe Financial Associates公司主席Al Boschulte稱,“但我們必須體認到,如果缺少一個匯整了主要載波的系統,就存在著被寬頻市場淘汰的風險。因此,對英特爾而言,投資Clearwire是最好的方式。”

ABI Research的Solis認為,由於英特爾曾在2004年投資Clearwire時,便設法說服該公司將OFDM技術基礎轉為接近802.16e的標準,因而此次英特爾的投資並不足為奇。Solis表示,在美國所有的WiMAX服務供應商新創企業中,Clearwire最合乎英特爾實現WiMAX前景規劃的要求。

In-Stat最新一份調查報告顯示,要真正在美國實現WiMAX全國性覆蓋還需要30億美元的資金投入。不過,據In-Stat稱,由於WiMAX還必須與DSL及有線網路展開競爭,因此到2009年以前,只有不到5%的美國寬頻客戶會採用WiMAX。

英特爾的一位發言人表示,啟動市場所需要的資金數額說明了為什麼英特爾必須要投資5億美元以上的原因。“WiMAX滲透到有線寬頻服務的時間可能很容易估計,”她補充道,“但是英特爾預計,WiMAX要達到普及仍將需要數年的時間。”

Clearwire的S-1檔案文件顯示,該公司目前在美國的用戶數目達8萬,在比利時和愛爾蘭為11,500。在美國,Clearwire的服務區域內潛在客戶達480萬。目前,Clearwire的足跡覆蓋了27個獨立的都會區域市場,其中包括200多個城鎮。

雖然該公司強調網際網路接取是其主要應用領域,但透過NextNet,它已設計出了具有QoS機制的系統,可以用來處理IP語音及可存檔的視訊點播型行動IPTV。目前由NextNet利用授權2.5GHz和3.5GHz頻段所開發的Clearwire系統,具有1.5Mbps的下行鏈路速度和256kbps的上行鏈路速度。

雖然Sprint可能在某些地區展開更大規模的測試服務,但Solis仍然認為,除非Sprint決定將Nextel技術與其American Telecasting公司的技術結合而成的系統升級到完整版的802.16e,否則該公司是不可能大規模推出WiMAX的。(Sprint在1999年收購了早期的MMDS專業公司American Telecasting。)

Sprint的一位發言人證實,該公司應該會在今年夏天決定所有的技術策略,緊接著是按提議作出詳細的網路設備要求。這位發言人表示,這將不僅是在2.5GHz頻段OFDM寬頻無線技術的評估,也是針對回程和行動接取,以及WiMAX、WCDMA、高速下行鏈路(及上行鏈路)封包接取,以及頻分和時分雙工技術等應用的廣泛競爭力分析。

美國電信市場要能超越目前Clearwire和Sprint所形成的格局之外再進一步的發展,這將必須取決於使更多廠商轉向統一的IP服務。摩托羅拉先進網路技術副總裁Bill Payne表示,由於IEEE受限於僅能為WiMAX硬體的PHY和MAC功能作定義,而WiMAX論壇成員則希望還能針對端對端服務加以定義,因此,WiMAX論壇網路工作小組所扮演的角色也就至關重要。

經理人觀點(0609A)

上網時間 : 2006年09月13日

“他們不得不進行許多額外的補強工作,以設法修復所發生的問題。” Shankar Krishnamoorthy

Sierra設計自動化公司技術長Shankar Krishnamoorthy指出,在進行65nm和45nm晶片設計時,需解決微影與時脈收斂的變異性問題。

“看來美國似乎將為中國打開一扇門,但是這扇門將會開放得多大呢?” 梅新育

中國商務部國際貿易研究員梅新育表示,美國政府計劃修訂的對中國出口新規定,是否可簡化美國先進半導體製造設備的進口仍不得而知。

“對於先進SoC而言,它可能成為主流記憶體。” Kazutami Arimoto

瑞薩工程經理Kazutami Arimoto聲稱,eT2RAM更適合現代的SoC解決方案,它透過多重電壓和其它的電源管理配置,保持功耗在控制範圍內。

“真正獲利豐厚的仍然是130nm和90nm製程節點。” Mary Ann Olsson

Gartner Dataquest的EDA設計研究中心副總裁Mary Ann Olsson透露,即使最先進的公司仍然利用90nm和130nm設計來賺取大部份的營收。

“ASI(先進交換互連)差不多已走到盡頭。” Kelly Ambriz

Vitesse Semiconductor行銷經理Kelly Ambriz認為,此技術看來已經失敗。

“這是一個非常令人頭痛的數學問題。” Paul Estrada

針對多重速率(multirate)設計,Berkeley設計自動化公司營運長Paul Estrada如此評論。

“如果我們不能了解合作的利益所在,那就太慚愧了。” Steve Ballmer

微軟執行長Steve Ballmer表示,該公司將與北電合作獲取更多專利,並開發軟體產品。

“基本上,消費者並沒有看到轉嫁成本的現象。” Mark Zandi

美國economy.com首席分析師Mark Zandi指出,儘管價格持續升高,但許多廠商已自行吸收成本上漲,並未把它們傳遞給終端客戶。

EDA產業全面投入解決當前的設計問題

上網時間 : 2006年09月13日

新製程節點激發EDA的創新,並因而推動內部和第三方工具開發的興起。專有工具可服務特定的設計需要,特別是在設計早期階段。但像可製造性設計(DFM)這種對營收具有重要影響的設計領域則必須採用最佳設計工具,以因應艱鉅的設計和製造挑戰,而這也是一般公司轉而求助於第三方工具的主因。

儘管先進的大型領導廠商能負擔得起內部自行開發工具的成本,但目前一般普遍使用的還是第三方的工具。經濟規模是一大主因,而其可靠性也是另一項考量。為因應不同設計專案的使用,第三方工具面對著不同的設計挑戰;因而也較為強韌可靠。此外,維持專有工具所必備的研發成本與資源也是驅使這些公司轉向第三方工具的一項因素。大部份的無晶圓半導體公司仍欠缺可建立內部EDA開發團隊所應有的合理規模。

市場上的一個跡象顯示,EDA創新一路高歌。DFM目前正經歷著EDA史上最快速的成長和普及率。但這種成長並不表示該產業忽略掉消費者的需求。設計者購買工具是因為工具能解決他們的問題,所以,目前的DFM產品顯然合乎設計者的需求。

電子系統級設計在從小規模、片段且單一用途的工具轉變為可提供更大生產力的複雜方法學時,都是以透過創新保持成長而來的。

EDA產業正全面投入於解決目前的設計問題。在該產業發展之初,創新就在產業的大、小新創公司中不斷地成長茁莊。根據Gartner Dataquest公司最近的市場佔有資料顯示出EDA產業獨特架構:3家收入超5億美元的大公司、若干收入在4,000萬~1.5億美元之間的中等規模公司,以及數百家小公司的收入在4000萬美元以下。據估計,該產業共有400~500家獨立的EDA供應公司。

根據Gartner Dataquest的看法,因為EDA產業的專業化分工,這些大大小小的公司得以共生共存。EDA產業包括63種不同的產品區分,並由不同公司為其提供不同的產品。大公司意欲涉足營收較高的領域,小公司則專攻細分市場;而帶來新奇方法學和創新工具的新興公司也不斷湧現。

因此,只要電子產業的設計複雜度仍然存在,EDA工具的創新便將持續開花結果。

Wally Rhines

董事長暨執行長

明導國際

PC產業面臨轉型 台灣IT產業將何去何從?

上網時間 : 2006年09月13日

隨著鴻海精密公司透過併購不斷地擴展其規模,從PC開始,現在不管是手機、液晶監視器、主機板、數位相機,或是通訊設備,幾乎到處都可以看到這個全球第二大電子製造服務商(EMS)的蹤影。這也是台灣IT製造業者積極轉型,追逐成長的一種縮影。但是對傳統以來以中小型企業型態為主的許多台灣電腦和週邊設備製造廠商來說,他們也都把鴻海視為其商業經營上的致命殺手。

的確,在大者恆大的產業趨勢下,IT製造業者勢必得持續擴充產能與規模,築起高聳的進入障礙與競爭優勢,以阻絕後進者的市場機會。所以,台灣的ODM廠商與電子製造服務(EMS)公司們在已經主導了PC、週邊設備、主機板和網路卡等產品的供應鏈之後;現在,他們也已開始滲透到光學驅動器等更多樣化的產業領域中。

多年來,這些IT專業公司們經由自我提升製造力和系統性能而不斷地擴張。那麼,專注於生產電腦及週邊設備的中小型企業將何去何從?一旦這些勇於開拓的廠商成為台灣IT業的基石,那麼傳統的週邊設備製造商將黯然失色。

隨著台灣IT產業的結盟,PC和週邊設備銷售也開始停滯不前。不久前,這些廠商們便從MP3播放器和USB驅動器等高價的產品中尋求避風港,然而,這塊大餅可分食的部份畢竟太少了。現在他們的目標便轉向爭奪網路設備這類更小的利基型產品上。

台灣中小型電腦和週邊設備製造商正轉向採用新產品的策略,但這些產品目前正處於早期發展階段,而且也還沒有相關的標準規格。例如,可攜式媒體播放器(PMP)即其一例。同時,這個策略需要在產品設計上大力投資,也必須致於改善半導體元件供應商與設計公司之間的關係。

台灣PC和週邊設備製造商所面臨的另一個嚴峻的挑戰是電腦、通訊和消費電子產品的不斷融合。在某些方面,通訊和消費電子產品的重疊性已高達60%。技術的融合也意味著更高的設計門檻與更激烈的競爭,同時,由於產品功能的重疊,再也沒有‘單純’的運算或通訊產品,所以不管是通訊或電腦業者,他們都會推出功能類似的產品,同樣地競逐消費性市場,自然也帶來更嚴峻的成本與產品週期壓力。所以,沒有足夠市場規模與技術整合能力的中小型業者將會首當其衝,營運更為辛苦。

中國人常說挑戰即機會,當然上述的這種挑戰也為PC和週邊設備製造商們帶來產品的多元化。但是,製造商們還必須具備對產品更深入的設計知識,並且能掌握其半導體組成元件的技術內涵。

藍芽技術、全球定位系統(GPS)與VoIP的興起已為通訊產品製造商帶來更多商機,但是對於台灣的PC和週邊設備製造商而言,目前我們還未見到該市場存在著什麼殺手級應用。

許多公司都在期待微軟新款作業系統Vista的發佈,希望它能為其新產品的開發注入更多機會。同時,隨著PC平台中整合了更多的新技術與功能,從遊戲機到音樂播放器等各式新興設備也已經駐足於PC門外。

在全球約有10億台PC正被人們所使用,估計全球每年的PC銷售量已達到2億台,因此週邊設備製造商可隨之銷售更多配套產品。但是在PC產業中探索新產品亮點的過程中,製造商們所採用的方式必須更加靈活多變。同時,在PC事業發展的重要十字路口上,設計創新毫無疑問地扮演著舉足輕重的角色。

在PC誕生25年的前夕,持續關注台灣IT產業價值鏈的關鍵部份如何重新打造自己,將會是一件有趣的事。

Majeed Ahmad

RFIC設計流程中的挑戰及解決方案分析

上網時間 : 2006年09月11日

近年來,行動通訊的市場需求成長迅速,目前的行動通訊系統已經可以使用成熟的訊號處理技術取得更高的資料傳輸速率。但新一代瞄準多標準與可重配置的無線系統設計難度正不斷提升。不同的通訊標準在中心頻率、訊號頻寬、訊息噪音比和線性度等方面差異很大。這對所有射頻(RF)前端建構模組的設計有很大影響,必須進行全面性權衡分析以選擇最佳架構,並為單獨的電路模組選擇合適設計規格。

隨著數位訊號處理的複雜度正持續上升。數位模組能夠部份補償由類比前端模組帶來的訊號損害。為了充分驗證複雜的數位補償演算法以及由相位噪音、非線性和失配等類比非理想特性所帶來的影響,數位和類比模組必須協同驗證。實現RF/基頻協同設計瓶頸是在射頻前端出現的GHz級RF載波訊號。為了在電晶體級對一個完整通訊鏈路的誤碼率(BER)和誤包率(PER)進行模擬,必須將已調訊號執行數千個週期,但這種做法成本很高甚至無法實現。

除了對實際設計進行設計規格確認的性能驗證外,另一個關鍵要求是對整個晶片的功能驗證。在數位控制電路(負責各種作業模式的使能,如上電、斷電、接收、發射和頻帶選擇等)和類比前端之間的介面實現錯誤是導致設計反覆的重要原因。

RFIC設計挑戰

IC設計工程師通常會恪守由系統設計師制訂的預算要求。他們也許能證明更寬鬆的IC設計規格也能達到系統級設計要求,但是在缺乏理論驗證的情況下,花費大量時間用於最佳化電路並不必要。由於需要不同的專業知識和工具,通常基頻和類比/RF兩部份是分開設計、模擬和驗證。系統級設計主要目標是找到一種合適的演算法和架構,以便以最低的成本實現所需功能和性能。

但是在實際實現階段,RFIC設計工程師仍需面對很多嚴峻挑戰。以無線收發器這種大型IC為例,較高的訊號傳輸速率使電路對寄生效應非常敏感,包括寄生電感和噪音等。因此,RFIC設計流程的實質是管理、複製和控制版圖後模擬及其效果,並在整個設計過程中高效地使用這些資訊。

RFIC設計還要求設計工程師具有RF領域的專業和獨特分析技術,這些跨越頻域和時域的分析方法選擇取決於電路類型、設計工程師技術水準、電路尺寸或設計風格。為了方便選擇,需用模擬方法提供一個無縫的整合環境。

在RFIC設計領域,整合也是大勢所趨。過去,RFIC被看作一個相對獨立的設計領域,現在,很多RFIC包含了ADC、DAC和PLL功能,以及在數位設計環境中製作並整合在晶片中的數位合成器。另一方面,RF模組也正被添加進大型SoC中以實現單晶片解決方案。採用系統級封裝(SiP)還可以整合其它功能,與RFIC和SoC設計方法一樣,採用SiP技術也會面臨相似的驗證問題。

一個全面的設計解決方案必須能夠解決這些挑戰,包括:

1. 為系統級設計和IC實現提供全面鏈接;

2. 在一個系統級環境下進行IC驗證,以充分利用現有的無線單元庫、模型和測試基準(test bench);

3. 支援在不同抽象級的全晶片混合級模擬;

4. 在經過最佳化的模擬時間內,在晶片級和模組級進行詳細的分析;

5. 可管理和模擬全部寄生效應;

6. 在適當的設計點,提供版圖自動化功能;

7. 支援在整個設計過程中多個層次的被動元件建模(passive modeling)。

必須在單一設計環境中滿足以上所有要求,這不僅有助於RFIC設計工作,而且有助於與類比/AMS和數位設計整合。在多個抽象級(包括晶片級和模組級)下,相同的設計可以獨立於實體整合策略之外,而被重覆執行以方便驗證及實現。

無線RFIC設計流程

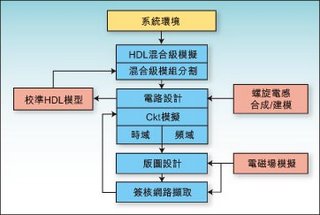

無線RFIC設計流程如圖1所示。該流程覆蓋了從系統設計到實現IC的全部過程。

圖1:無線RFIC設計流程

1. 使用系統級資源

來自系統設計流程是最高的抽象層次,系統級設計描述可作為頂層晶片的可執行測試環境。週邊系統的模型可與晶片的高級模型整合以產生一個可執行的設計規格。系統設計要求可作為最早的設計規格以驅動晶片級設計要求,並最終成為可再使用的測試基準和回歸模擬模型。部份系統級的IP資源也可用來確定系統的性能參數如EVM、BER和PER。

混合級模擬有助於系統和模組設計工程師之間共享資訊。為了保證系統環境和IC環境之間的介面,多模式模擬解決方案必須是適合任何的語言的,包括C/C++、SystemC、SystemVerilog、數位/混合訊號/類比行為級HDL語言以及SPICE,並能為跨多模的電路設計提供不同的專用引擎和演算法。

2. 設計規劃和模擬策略

一個複雜設計能否成功很大程度上取決於預先規劃的徹底性。如果在設計初期就對設計頂層要求、模組級要求和混合級策略有清晰的規劃,‘從兩端到中間’的設計方式將保證所有模組都能滿足主要的設計規格要求,並能更靈活的安排進度。因此,全面的模擬策略和建模規劃非常關鍵。在成功實現了高階可執行規格後,設計過程將深入到設計中某些特定區域,並制訂該區域的驗證計劃。驗證計劃會規定測試如何執行,並確定哪些模組在測試中處於電晶體級。工程師要注意在設立和編寫模型程式碼時不要過分複雜化,在開始時只需簡單的模型和必要的模型特性。

正式的規劃過程是實現高效、全面驗證的前提,有助於在設計初期擷取更多的設計錯誤並減少設計迴圈次數。可以在最初對高階系統描述採用模擬和測試計劃,這樣能快速實現除錯。經驗證有效後,它們會被用於模組的混合級模擬,以減少在設計週期後期出錯的風險。

3. 多模式模擬環境

對加入系統級測試基準的RFIC進行HDL建模是自上而下設計過程的開始。這包含所有RF模組,以及所有的類比部份和/或數位模組。第一步是在一個頂層測試基準中對全晶片進行行為級建模,並進行一些系統測試,如EVM和BER。這會對IC設計的模組分割、模組功能和理想性能特性進行驗證。這種行為模型可作為混合級模擬的基礎,任何模組都能以電晶體級形式插入並在頂層環境下進行驗證。此外,全晶片和系統級的設定可作為一種回歸模板(regression template),隨著模組逐步成熟而不斷用於驗證,這也為整個設計過程提供了一種不斷演進的設計方法。這種方法能在設計初期發現大量問題,並保證有充足的時間來解決這些問題。同時,不同的模組也能以各自的進度平行開發。

在整個模擬環境中,同一電路有不同的分析視圖,其中可能包括行為級視圖、版圖前電晶體級視圖和有關寄生效應的多種視圖。隨著模組的逐漸成熟,需增加更多的電晶體級資訊以測試RF/類比介面和RF/數位介面。同時還需使用混合訊號模擬器來處理類比、數位和RF描述,並將行為級和電晶體級抽象混合。為每一個模組或子模組選擇合適的視圖,管理執行時間和精確度,並在二者之間進行權衡,這可以透過模擬選項來實現,例如將電晶體導入快速Spice模擬器中,或將電晶體保持在全Spice模式下。這種配置對電路和介面的感應度有很高的依賴性。由於需要重覆利用這些配置,對這些配置進行高效的管理顯得很重要。這也提供了一種非常有效的機制來設立支援ACD的持續回歸驗證。

4. 模組電路設計

接下來開始電路的初步設計,首先進行電路研究並了解性能規格要求。這種早期研究有助於形成頂層的版圖規劃,對RFIC來說頂層版圖規劃對噪音和模組級互連非常敏感。在該階段,可嘗試對螺旋電感等被動元件進行合成以滿足規格要求,並在晶片上進行最初的佈局。這個階段可進行兩項重要工作:為螺旋電感製作早期模型,並在模組級版圖完成前用於模擬;對螺旋電感之間的互感進行初始分析。可在該階段為所有的電感製作元件模型以用於模擬。

可依照設計工程師偏好的方法進行模擬,頻域或者時域模擬均可,設計工程師須考量電路特點、模擬類型和模擬量等因素後再決定。一個單一的製程設計套件和配套設計環境可協助設計工程師選擇合適的模擬演算法。可根據模擬類型以合適的方式顯示結果。當模組級的電路完成後,設計工程師可以在頂層環境下使用行為激勵和對週邊晶片的描述來驗證這些電路。

5. 實體實現

版圖設計自動化功能(自動佈線、連通性驅動和設計規則驅動的版圖設計和佈局等)是非常高效的。由於緊密地結合了原理圖和設計約束規則,版圖設計自動化能大幅提升工作效率。佈線器能夠解決差分對、屏蔽線的佈線問題,並支援手動設置每一根走線的佈線約束。這就使實體設計過程像前端設計過程一樣具有可重覆性。雖然在初期要投入一些時間來設立這些工具,但它們在以後的設計過程中都是可再使用的。

6. 寄生參數擷取

在版圖完成後,電磁場模擬(EM)可為被動元件產生高精密度的模型。例如,可選擇幾個螺旋電感作為EM模擬的關鍵對象,具體做法是:用螺旋電感替換在設計過程中已經製作的一些模型,混合併匹配現有的模型。設計工程師需要全面監控螺旋電感的建模過程,並對執行時間和精確度進行權衡。

基於網路的寄生擷取是隨版圖出現後在整個設計過程中最重要的環節。RF設計對寄生效應非常敏感。由於設計工程師能掌握任何區域、走線或模組的相關寄生資訊,因此管理不同層次的寄生參數的資訊就變得更為重要。不敏感的走線只需要RC參數,而敏感的走線則需要RLC參數。具有螺旋電感的走線能以RLC和電感參數的形式擷取出來,甚至可對最敏感的走線添加底板效應。同時,這些走線可以與被動元件的元件模型混合匹配。

當頂層版圖實現後,噪音分析,特別是底板噪音分析可保證有噪電路(如數位邏輯和PLL)不會影響到高敏感的RF電路。設計工程師可對此進行檢查,如果關注的電路區域已被影響,設計工程師還可修改版圖規劃或在有噪電路周圍增加保護帶。然而,想在電晶體級對整個電路進行模擬或包含所有的寄生資訊往往是不切實際的。一種解決方法是擷取行為模型,但這會忽略不同模組間連線的寄生效應,因此必須支援層次化的擷取能力和設計模組間連線的寄生參數擷取。

7. 校準HDL模型

在模組開發完成後,可根據關鍵的電路性能參數對最初的行為模型進行反標注,這樣可實現更為精確的HDL級模擬。雖然並不適用於所有效應,但是這種方法能以更少的執行時間成本獲得更精確的性能資訊,並能加速驗證,減少全電晶體級驗證的工作量。

用混合級模擬對模組進行驗證有三個步驟。首先,在對模組功能進行驗證時,要在系統級模擬中包含一個理想化的模組模型;然後,用這個模組的網表替換理想化模型來驗證模組的功能。這樣就能檢測出模組缺陷給系統性能帶來的影響。

最後,用一個擷取模型代替模組的網表。透過對網表和擷取模型的模擬結果進行比較分析,可以對擷取模型的功能性和精確度進行驗證。在以後對其他模組進行混合級模擬時使用經過驗證的擷取模型而非理想模型能提高其有效性。

如果作業合理,自下而上的驗證方式能對大型系統實現更詳細的驗證。由於去掉了實體實現的細節而僅保留行為細節,行為模擬的執行速度非常快。隨著模組逐漸成熟,由自下而上驗證過程產生的行為模型越來越有用,並適用於第三方IP驗證和再使用。

對於包括射頻前端的無線系統來說,自下而上的驗證過程是驗證大型系統性能的必然方法。如前所述,電晶體級的RF系統驗證需將調變訊號執行數千個週期,這往往是不切實際的。用先進的包絡分析技術替代傳統的瞬態模擬只能將模擬速度提高10-20倍。即使將傳統的通帶模型用於自下而上的擷取技術,由於RF載頻仍然存在,也無法將模擬速度提高到令人滿意的程度。只有將自下而上的模型擷取技術和複雜的基頻或低通等效模型結合,載波訊號才會被有效抑制,其模擬時間才足以實現全晶片級的誤包率分析。

為所有模組都產生行為模型是一件耗時費力的工作,而且只有極少的設計工程師具有這種專業技術。而自動化的工具和方法學能夠根據特定應用和技術需要,借助經過驗證的精密度和開放API來修改現有模板以產生詳細的行為模型。

供稿:Cadence公司

GDDR3將3D繪圖應用性能發揮到極限

上網時間 : 2006年09月11日

記憶體頻寬對快速提升桌上型和筆記型電腦中繪圖系統的3D渲染性能具有關鍵作用。過去5年來,高階繪圖系統中的記憶體頻寬每年增加30%。繪圖記憶體系統頻寬已超越了PC主記憶體。為滿足這些頻寬要求,必須為繪圖記憶體定義專門的I/O標準。而自2005年起,新的GDDR3標準在繪圖市場上取得了突破性進展。

最早的繪圖記憶體與標準的通用DRAM有很大的區別。這些早期的繪圖記憶體透過專用功能支援3D渲染和顯示處理。歷經一代代發展,繪圖記憶體逐步轉向通用的標準DRAM。邏輯處理功能最終全部轉移到GPU內進行處理,繪圖記憶體則專注於作為DRAM的核心功能。因此,對這種繪圖記憶體的頻寬需求急劇成長。

在1990年代末,通用的標準DRAM已無法滿足繪圖處理器的頻寬需求。記憶體成為系統瓶頸,因此,x32 GDDR記憶體遂應運而生。當時,英飛凌(前西門子半導體公司)推出了雙倍數據速率繪圖RAM,其32Mb DDR-SGRAM大幅提升了速度;而2001年,英飛凌再度推出了128Mbit(4Mx32)的繪圖DDR記憶體。

英飛凌的128Mb GDDR採用BGA封裝,與TSOP或TQFP封裝相較,BGA封裝具有尺寸優勢,它在繪圖卡上所需空間僅有TQFP封裝的一半,因此相當適合筆記型繪圖系統。BGA封裝的第二大優勢是能顯著減少所有訊號與地址線上的電氣寄生效應。電氣寄生效應的降低是提高數據速率的必要條件。

隨著128Mb GDDR的推出,GDDR標準也宣告結束,因為GDDR標準無法滿足日益提高的頻寬要求。繪圖產業需要一個更先進、為更高數據速率最佳化的新標準。而GDDR3則是替代GDDR的全新標準。

GDDR3標準

GDDR3標準借鑒了通用DDR2的多種特性,並進一步最佳化以獲得更高的數據速率和更低的功耗。與GDDR相較,GDDR3的主要創新表現為:工作電壓從2.5V下降到1.8V;內部訊號端接取代了GDDR中未端接的訊號線;動態控制阻抗的輸出驅動器;4位元預取和單向單端數據閘控。這些特性實現了更高的數據速率、更好的訊號完整性和更低的功耗,因此GDDR3記憶體可獲得比GDDR和DDR2標準高得多的數據速率。

內部訊號端接:隨著傳輸頻率的上升,訊號線必須用電阻端接,以防止反射訊號干擾正常訊號而影響訊號品質。GDDR端接是透過外部電阻實現的,該電阻焊接在靠近記憶體的PCB上。外部端接可以略微擴展GDDR的頻率範圍,但該類端接方案不能滿足提升到高達800MHz甚至更高頻率範圍的GDDR3所需的訊號完整性。因此GDDR3使用內部訊號端接,其端接電阻整合在記憶體晶片內部。

支援可靠高速的點對點傳輸的另外一個重要功能特性是具有自適應阻抗的Vddq端接。GDDR3的I/O介面是一個匯流排兩端都被端接的偽開漏邏輯電路:一端是40歐姆阻抗的動態控制驅動器,另外一端是具有60歐姆訊號線端接的接收器。

在互動式3D遊戲中,繪圖運算可分成幾個順序執行的基本步驟。在第一個步驟中,根據遊戲者所下的指令結果運算產生3D場景。3D場景代表虛擬3D世界中所有物體的排列和位置資訊。這部份運算是由PC中的CPU完成的。然後CPU將3D場景傳遞給GPU。GPU的任務是將3D場景轉換成顯示器可以顯示的2D影像。GPU執行的這個任務被稱為3D渲染。

在產生實際影像時必須考慮很多效果,如顏色、紋理、多個擴展光源、陰影、反射、透明、光線吸收、不透明材料等。要實現這些效果就要求強大的運算能力以及寬的記憶體介面,以便在最短等待時間內完成對記憶體的隨機存取。所有這些運算必須即時完成,其每秒運算能力必須超過40個訊框。

表1:GDDR、GDDR3和DDR2標準比較

整合與獨立型繪圖設備

一般來說,繪圖系統可以分成兩大類,即整合繪圖系統和獨立繪圖系統。在整合繪圖系統中,繪圖處理單元嵌入在位於筆記型和桌上型電腦主機板上的PC晶片組內。對於紋理儲存和緩衝記憶體,這些整合系統使用PC的主記憶體。這一做法從兩方面限制了3D繪圖渲染性能。首先,最大記憶體頻寬受限於標準主記憶體頻寬,其次,繪圖系統必須與CPU以及PC上同時存取記憶體的其它客戶程式共享這個頻寬。

獨立繪圖系統由實際上分開且獨立工作的繪圖處理單元,以及與獨立GPU直接相連的專用繪圖記憶體組成。獨立繪圖系統透過標準的PCI-E(以前是AGP)匯流排與PC晶片組連接。這些獨立GPU的3D處理性能目前已遠超過整合繪圖處理器性能,對記憶體頻寬的要求也是如此。基準測試顯示,獨立繪圖系統的性能超過整合系統3到20倍。記憶體I/O技術和記憶體頻寬在實現這個性能飛躍中具有關鍵作用。

高階繪圖卡使用專門的x32結構繪圖記憶體。如今這些系統採用500到800MHz時脈頻率的GDDR3記憶體,組成高達512MB的訊框緩衝記憶體。這些配置向GPU提供的記憶體頻寬高達410Gbps,相當於目前最先進的PC主記憶體頻寬的12倍。最新的高階筆記型電腦繪圖系統採用500MHz GDDR3記憶體組成256MB訊框緩衝記憶體,向GPU提供的記憶體頻寬仍可達到這些筆記型電腦中主記憶體頻寬的5倍。

主流繪圖系統通常採用x16結構的記憶體元件。大多數新的主流繪圖系統採用時脈頻率約400MHz的DDR2 I/O技術。這些系統的性能仍明顯高於整合繪圖系統。

整合與獨立型繪圖系統前景

據Mercury Research公司調查,PC中獨立繪圖系統的市場佔有率在過去幾年中約為40%~45%。像Windows Vista這類3D作業系統可能會提高對普通PC的3D渲染性能需求,因此可能會影響獨立繪圖系統的市場佔有率。

Mercury也預測,2005年的獨立繪圖系統市場有1.5億套,而整合繪圖系統有1.6億套。其中2,200萬套獨立繪圖系統銷售給筆記型電腦,8,300萬套獨立繪圖系統銷售給桌上型電腦。

今後對不斷增加的記憶體頻寬的要求仍將繼續。提高影像品質的新技術推動了頻寬的增加。即將來臨的高解析度顯示將進一步提升解析度和每訊框被渲染和顯示的畫素數量。像可渲染每個密集光源之光暈效應的高動態範圍渲染(HDRR)等新興渲染技術,正不斷提高對每畫素執行運算的複雜度。

除了PC繪圖系統外,繪圖DRAM還存在著其它一些既有和即將出現的市場。新一代主要遊戲機都將使用GDDR3繪圖記憶體。家庭內使用的媒體中心和媒體網路閘道也將包含強大的繪圖性能,因此也需要繪圖記憶體。像Windows Vista這種新3D作業系統將把3D渲染性能的需求擴展到幾乎每台新的PC中。

作者:Christoph Bilger

繪圖記憶體行銷經理

英飛凌科技

為可攜式應用選擇先進節能技術

上網時間 : 2006年09月11日

包括無線手機、智慧型手機、PDA和媒體播放機在內,新一代可攜式消費電子產品均可以提供更豐富的功能、更強大效能、與更精巧的體積。這些擁有最新功能的裝置包括解析度超過300萬畫素的相機、高功率的相機閃光燈LED或氙氣燈、先進的音訊和喇叭功能、無線電話以及可隨身攜帶的高解析度液晶電視,都需要更多的電力供應。

由於上述設備對電力的需求愈來愈迫切,因此,靜態與動態的電源需求管理不僅對基於電池供電的產品極為重要,對於設計人員也提出了艱鉅挑戰。隨著可攜式裝置的功能日益豐富,它們的耗電總量也在快速增加中,這也使電池的壽命明顯縮短。

此外,類比與數位基頻元件的處理器單元、中央處理器主機以及繪圖/音訊處理器的先進程度和功能整合度正不斷提高。隨著這些元件所整合的功能日益增加,它們需要更多組電源,每一組電源也需要提供更大的電流。

多數可攜式消費產品通常只會使用一顆標準的高效能鋰離子電池。由於這樣的電力供應相當有限,製造商必須判斷客戶是否願意為更多功能而犧牲部份電池壽命,還是寧願減少應用產品的功能和電力需求。然而今日的客戶自有主見,他們希望魚與熊掌兼得:亦即在不縮短電池壽命的情形下提供更先進的高階產品。

新興節能技術

許多技巧都可用來解決這些設計困境,例如,許多半導體廠商正設法降低特定效能下的耗電量以滿足處理器要求。以TI為例,其DSP或OMAP核心的標準數位元件製造技術除採用90奈米技術外,新一代65奈米技術也已在2005年底量產。製程技術每進步一個世代,電晶體密度通常就會增加一倍,相當於將設計縮小為原來的一半,電晶體效能則提升將近四成。這種做法可大幅降低核心的操作電壓,電流需求則大致保持相同或升高。另一方面,它會造成漏電現象更嚴重,甚至抵消原本帶來的效能優勢。還有許多類比與數位元件省電技術是與它們的生產製造無關,例如多種低耗電模式,時脈閘控以及電壓與頻率的動態調整,這些技術都在設計中扮演重要角色。

要滿足電源需求並克服省電挑戰就必須發展新的生產與製程技術,TI最近針對DSP和OMAP處理器所推出的新技術SmartReflex就是一個例子,它不僅將矽智財層級的靜態漏電大幅減少1,000倍,還能調整不同元件和系統建構模組的耗電量與效能,同時利用一組電源管理單元把電路分成多個電源區來各自管理。

類比與數位省電功能

整體而言,SmartReflex可以減少耗電總量、實現系統效能最佳化、並延長電池壽命。它會偵測元件的工作量、操作模式和溫度,然後利用多種智慧型和適應性硬體與軟體來動態控制電壓、頻率和電源,包括動態和適應性電壓調整、動態電源切換和待機漏電管理。此外,動態電壓調整也會用到外部的電源管理元件和軟體。舉例來說,核心供應電壓可隨著處理器負載不同而調整以便提供最大效能或降低待機耗電。

系統可視需求選擇分離式低壓降穩壓器、中等程度耗電或低耗電的直流轉換器、多通道電源管理元件或其它零件來提供電源給電路板和處理器。電源管理設計須能針對任何處理器提供必要的電源以及正確的電壓和電流。所有處理器和電源管理元件通常都會支援低負載或待機模式,只要應用被切斷電源或進入預先設定的省電模式,電源電壓就會下降,電流消耗則減至最少;在理想情形下,每顆元件的電流只有數個μA。這些做法基本上都屬於靜態電源管理,它們在電源管理設計完成後就無法繼續影響電源的電壓值。

近年來,市場上已出現內含I2C匯流排的低耗電直流降壓轉換器和高整合度多通道電源管理元件。分離式電源管理元件內建串列介面後即可提供許多新功能,例如透過標準串列I2C介面把軟體工具和處理器控制功能結合在一起後,數位和類比電源管理元件之間就能以前所未有的超高速率交換資訊,使系統能於執行中隨時調整電壓、電流和功率預算。除此之外,軟體控制的電源管理與監控也將得以實現,設計人員也能在現有的全負載操作模式與系統待機模式之外實作更多種省電模式。

圖1:SmartReflex技術為可攜式裝置提高節能效率

動態電壓調整

I2C介面共有100kbps和400kbps兩種不同的傳輸速率。隨著分離式低耗電直流轉換器和電源管理元件開始內建I2C介面,設計人員現已能準確地動態調整分離式電源管理元件的輸出電壓以及任何處理器單元的核心供應電壓。這類設計需要高速直流轉換器,例如使用開關頻率3MHz以上的轉換器以確保快速的訊號暫態響應。此外,低耗電直流轉換器或電源管理元件還應提供PFM或Forced-PFM等不同操作模式,這樣它們才能自我調整或是透過I2C控制訊號配合某些系統電源組態。

這類設計可讓系統在不影響整體表現的情形下精確滿足其效能需求。這能將每一種操作條件或處理器模式下的電力消耗減至最少,進而延長電池壽命、減少元件產生的熱量並增強整體系統效能。

此處以低耗電直流電源轉換器TPS62350說明SmartReflex技術。

圖2:TPS62350在鋰離子電池的輸入電壓範圍內供應800mA輸出電流

圖3:高整合度的TPS65020可透過I2C介面動態調整主要直流轉換器輸出電壓

這款單通道降壓轉換器採用體積精巧的12隻接腳晶片級封裝(CSP),能以95%的轉換效率在一顆鋰離子電池所提供的輸入電壓範圍內供應800mA的輸出電流。它還可透過I2C介面以最低0.6V的步階值來調整輸出電壓,使它能支援新一代的處理器和供應電源。這款可程式直流電源轉換器能大幅延長3G智慧型手機、PDA、數位相機和其它可攜式應用的電池壽命。

利用I2C介面減少耗電的另一種做法是使用TPS65020之類更複雜的元件。TPS65020是功能整合度極高的六通道電源管理晶片,內含三組效率達97%的低耗電直流電源轉換器和三組低壓降轉換器。舉例來說,TPS65020可透過I2C介面動態調整主要直流轉換器的輸出電壓,該電壓通常做為處理器核心的電源。另外兩組直流電源轉換器則可用於I/O電源供應、記憶體或其它功能。除此之外,TPS65020還能透過I2C介面將內建的三組低壓降穩壓器或直流轉換器等不同功能模組的電源切斷,這種做法可以減少整個電源管理元件的耗電或散熱,同時大幅降低靜態電流消耗。

多數的分離式直流電源轉換器、電源管理元件和低壓降穩壓器還會提供獨立的使能/禁能接腳,這使它們能夠在現有的處理器控制介面外獨立操作以便提供最強大的彈性和最方便的使用能力,同時讓其它新型省電技術也能夠繼續使用。

本文小結

除了前面介紹的省電方法外,新製造技術也會在未來扮演重要角色。隨著半導體技術逐漸從90奈米升級到65奈米和更精密的製程,此處介紹的省電技術實作將變得更為重要。除此之外,DSP核心和分離式電源零件之間通訊量也會增加,以便支援彈性的動態電源調整和軟體控制型電源供應機制。總而言之,這些增強功能和方法必須能夠完美配合,這樣系統才能提供最強大效能和最長電池壽命,進而讓使用者獲得最大好處。

作者:Alexander Friebe

德州儀器公司

越大越好? PC記憶體到底需要多少容量才夠用?

上網時間 : 2006年09月13日

多少記憶體才夠用?這是一個幾年來困擾著我和其他成千上萬電腦用戶的問題。迄今為止,真正讓我滿意的回答並不多見。這是一個特別重要的問題,因為記憶體的類型(無論是DDR、DDR2或其它類型)──都是由主機板和你的系統所採用的處理器決定的,你只能依據你的新機器來選擇所需要的記憶體的大小(或者之後再擴充)。

然而,要計算出多少記憶體才夠用並不容易:電腦記憶體就是這種情形。你所進行的工作以及所使用的軟體,都是決定最佳記憶體大小的因素──而它們會因PC不同而不同。例如根據微軟(Microsoft)的消息,執行專業版Windows XP作業系統所需要的就是“128M RAM以上的記憶體(最小支援64M;可能限制性能和一些功能)”,對處理器效能也有一個最低限制,但是有時你的處理器會遠遠超過那個最低限制要求。

所以說,我那台老舊而毛病不少的IBM ThinkPad 600X (記憶體64M)是可以執行Windows XP Pro。別笑!它真的可以…在某種程度上。通常Microsoft Word和Lotus Notes都可以平穩執行,但這就是你將獲得的最佳性能。Windows是種狡猾的軟體,如果看起來記憶體不夠的話,它就會速度越來越慢,直到整個螢幕停止,然後就開始把你的硬碟當記憶體用,並根據需要從硬碟來回檢測數據。不同之處在於速度(甚至整體性能)將像散步一樣慢。

對所需要的記憶體做測試

但是,人們關心的是多少記憶體才是最理想的。為了找到答案,我決定採用一個典型的媒體中心系統(Media Center system),並把記憶體從512M(實際上是比64M更為合理的記憶體基線)到2GB逐級增加。512M是大多消費者主機板所支援的最大記憶體的一半,而對多數電腦則絕對是最大的記憶體。

為此,我從Crucial Technology獲得了四片Ballistix 240接腳 DIMM、DDR2 PC2-6400記憶體模組(P/N # BL6464AA804)。因為這是高性能模組(連同散熱器),它可能很貴──每個模組高達100美元。你也可以找到替代品,像Crucial的標準PC2-4200模組(P/N # CT6464AA53E),每一個模組的價格不到40美元。

我使用了兩種軟體──COSBI OpenSourceMark (OSMark)和Ulead VideoStudio 10 Plus──來測試附加記憶體對我的電腦的影響。

OSMark是同步基準──那意味著在軟體中沒有實際的商業應用。人們設計OSMark就是為了測試所有的子系統(CPU、記憶體、繪圖晶片、硬碟),並通過組合及對那些不同的結果加權,然後從中得到唯一的特性數。VideoStudio是一種實際的應用軟體,我用它來從1小時的擷取電視視訊中分離43分鐘的視訊,然後,在剔除商業廣告之後,重新整合為完整的節目。電腦處理這樣的任務是舉重若輕。

順便說一下,我將在系統中做的其它變化──除了添加更多的記憶體──就是從雙通道記憶體架構來回存取數據。不提高到雙通道的速度可以嗎?沒有問題!

雙通道(dual-channel)就是成對地使用記憶體模組,而不是使用單一記憶體元件。為什麼這樣做好?以撲克牌為例,如果你只用一隻從一疊撲克最上層取一張牌,放在你身邊,然後再用同一隻手取下一張,直到所有的牌都拿到你身邊;跟兩隻手一起作業來比較,一隻手取撲克牌,另一隻手接著取下一張,那麼你完成同樣事情的速度就提高了一倍。

進行記憶體基準評估

具有512M記憶體的電腦產生的OSMark的結果是1,053──如果你跟其它高性能電腦相較就不高。幸運的是,這台特別的電腦並不是用來表現效能的,我們只是用它做娛樂中心,而且還有改善的空間。當系統記憶體超過1GB時,基準測試就再也不能測量出所改善的性能了。

採用所安裝的兩個512M記憶體模組(總共1GB)而不用主機板的雙通道性能,OSMark數據被拉高到1,074。分數更高,但是改進不大。然而,當我切換兩個模組以便它們利用雙通道的優點時,OSMark數據跳到了1,111。

換言之,從512M轉移到1GB雙通道模式,可以把性能提高15%;雖然採用相同的記憶體,如果不採用雙通道模式,意味著只有不到2%的性能提高。只是重新換個位子,就得到了不錯的結果!

既然認為記憶體越多就越好,我在電腦加入了第三條記憶體模組,使之達到總共1,536MB。然而,這會是對雙通道工作方式的誤用──雙通道需要採用數量為偶數記憶體模組。這次OSMark給系統打的分是1,112。記憶體增加了512M,而性能僅僅提高了一點?這幾乎沒有辦法讓你在更多的記憶體上花錢。

所以,我安裝了第四條並且是最後一條512M記憶體,因而把所有記憶體都恢復了雙通道作業。此時,OSMark產生了1,112的結果,一定很驚奇吧?這就是你為什麼從來不僅僅依賴基準比較的原因。

所產生的結果顯示:記憶體超過了基準的測量範圍。看來OSMark不需要1GB以上的記憶體來執行,所以超過1GB之後,再增加記憶體都看不到性能的提高。你怎麼證明情況就是這樣呢?透過切換到實際的應用:VideoStudio 10 Plus。

現實生活中的記憶體

我的43分鐘視訊檔的播放時間(rendering time)揭示了非常相同的規律。當採用單通道記憶體安排時,從512M跳到1GB幾乎沒有區別。實際上,對512M記憶體,視訊檔的播放時間為35分2秒(2,102秒);而對1GB記憶體,播放時間為34分50秒。

當我重新安排記憶體為雙通道配置時(記憶體成對以色彩編碼,以便你能告知在哪裏安裝記憶體),播放時間下降到31分45秒(1,905秒)。性能提高了4分鐘以上。如果你一天播放幾次,或每週幾次,那麼,你一年內就能夠節省幾天時間,而你所要做的只是把記憶體模組放置在合適的位置。

採用更大的記憶體會怎麼樣?當我插入第三條512M記憶體模組時,播放時間實際上慢了17秒,為32分2秒(1,922秒)。為什麼?這是一個教訓-─因為我已經擾亂了雙通道的工作。

當我插入第四條512M記憶體以平衡雙通道的安排時,播放時間下降到30分31秒(1,831秒)。播放時間的進一步減少正是我需要證明的:OSMark合成基準沒有使用我插入的1GB以上的那部份記憶體。

我可以再插入更多的記憶體以觀察播放性能的進一步改善嗎?答案也許“是”。但是,從那時候開始,我已經觸及收益遞減的法則。因為我只有4條插槽可用,為此我需要扔掉兩條我正使用中的記憶體模組,然後用更大的記憶體來替代;例如,用兩個1GB模組替代。那就是購買新的記憶體的主要費用,並且浪費了舊記憶體模組的投資。

除非你對視訊播放時間要求很高(或任何工作量很大的應用),升級記憶體所提高的性能可能不值得所付出的成本。為什麼?現在,像我使用的那種單512M記憶體模組的成本是105美元。記憶體的價格是不穩定的,所以,實際成本可能會變化。切換到採用雙通道模式的1GB記憶體,性能提高很大,而我的最初記憶體成本加到210美元。把該成本再加一倍(達到420美元),就可以安裝2GB記憶體,因而獲得更低的投資回報。

如果你採用2GB以上的記憶體,你將花費大約2.5倍以上的投資。記住,為了達到3GB記憶體,你要丟棄最初的記憶體模組,因而損失210美元;而替換為每條成本為186美元的兩個1GB記憶體模組。增加這些記憶體總共要花費1,192美元,而最好情況下,性能僅僅提高一點點。

結論

不幸的是,雖然我已經證明了雙通道是首選的使用模式,但是,我也加強了記憶體數量要“因地制宜”的觀念。它完全取決於你需要記憶體做什麼。對於大多數情形,你可能已經達到了記憶體增加到2GB之後的價值點。實際上對於廣大的業餘愛好者來說,僅僅1GB的記憶體就可能引發嚴重的爭論。

對於視訊播放、大型電子資料表、繪圖影像處理和類似需要大量記憶體的應用,更多的記憶體只能把性能提高到某一臨界點;在臨界點之後如果再增加記憶體,你無異於把你辛辛苦苦賺來的鈔票投進碎紙機。除非你不在意投資回報,你需要做一些工作來運算出何時你才能達到臨界點。

奈米微晶電路可望革新半導體製程

上網時間 : 2006年08月15日

半導體的未來將不再侷限於晶片,取而代之的是在晶片上製造電路,並將之焊接在印刷電路板上,加拿大的研究人員建議了一種直接將透明的‘溶液製程’(solution processed)電路塗佈到元件表面的方法。從大尺寸顯示器用的射極到用於噴渡式太陽能電池的檢測器半導體電路,都能大幅降低電子元件成本。

首個受益的產品可能是軍事用夜視鏡,可能改善約10倍的靈敏度,而且較目前的產品更便宜。但多倫多大學的研究小組表示,這項研究才剛起步。

“我們稍早前提出了首個採用溶液製程的高效能半導體元件,”該研究小組領導人Ted Sargent表示。Sargent是多倫多大學電子工程教授兼加拿大奈米技術研究工程主席。“我們的溶液製程檢測器較傳統磊晶生長的半導體元件靈敏度高出10倍。”

2003年,Sargent的小組展示了首個基於溶液製程的紅外線發射器。去年,他們提出了首個基於溶液製程的紅外線檢測器。然而,與傳統紅外線檢測器晶片相比,其光檢測器的效能卻令人感到沮喪。

“當我們提出首個溶液製程的紅外線光檢測器時,這些元件證實了我們構想。它們的效率遠低於任何成像應用所需要的,”Sargent說。“現在,我們已大幅改良了導電性能,並將檢測器的敏感度改善了兩個數量級(大約是百倍之多)。”

Sargent表示,除了可便宜地量產外,其光檢測器的材料能使當前使用紅外線的軍用夜視鏡靈敏度增加10倍,當然也包括使用紅外線以觀察皮膚下影像的生物成像系統在內。

Sargent獲得了多倫多大學博士研究員Gerasimos Konstantatos的協助,共同進行這項研究。

Sargent的研究小組承諾將加快採用基於溶液製程電路的速度。Sargent聲稱,透過去除有機聚合物並改為採用膠質硫化鉛奈米顆粒(colloidal lead sulphide nanoparticle),低成本的溶液製程電路能實現與矽晶片相同的效能。

Sargent的有機半導體溶濟原始分子式是一部份的聚合物與一部份的奈米顆粒──這是極微小的‘量子點’,其直徑為2~6奈米,平均分佈在導電性聚合物矩陣中。

由於奈米顆粒比通過它們的電子波長小10倍,因此電子必須再壓縮以符合內部的微小奈米顆粒。此一過程將引發更活躍的半導體行為,如光致電壓(photovoltaic)、光致發光(photoluminescent)與光電導(photoconductive)等效應。

然而,與半導體奈米顆粒相比,聚合物本身的傳導性相對較低,這減小了Sargent的有機溶液製程電路的效率及靈敏性。Sargent試著增加更多奈米顆粒以緩合‘有機問題’,直到他找到了完全消除聚合物矩陣的方法。

現在,Sargent混合了純半導體奈米顆粒與油酸(oleic acid),並將之旋鍍在玻璃基板上。在浸泡於甲醇中兩小時後,溶濟會蒸發並生成800奈米的純半導體奈米顆粒層。

“我們正進入全新的幾合學與材料混合世代,”Sargent說。“過去,我們一直採用奈米晶體聚合物的複合物,但這是無聚合物的純奈米晶體元件。”

Sargent過去曾提出其檢測器同樣可配置為紅外線太陽能電池的報告,但為了實現純奈米微晶(nanocrystalline)元件的高靈敏度,研究人員放棄了自光產生電能的光致電壓(photovoltaic)方法,轉而針對光電導操作模式配置奈米顆粒,從而減少阻抗並藉由光增強傳導性。

“我們相信,這種材料系統非常適合光電導模式,在照明下其傳導性將獲得提升,”Sargent表示。

(R. Colin Johnson)

新聞評析-高容量microSD為新帝金母雞主宰50%獲利來源 惟缺貨嚴重、台模組廠調貨貼牌應急

(記者連于慧∕特稿) 2006/09/13

儘管新帝(SanDisk)穩坐全球快閃記憶卡龍頭,其最主要的獲利仍是源自幾乎獨佔市場的高容量microSD,1GB和2GB容量的microSD價格幾乎是一般SD卡的2倍,新帝享受的毛利率高達50%,儼然是新帝的金母雞,據了解,光是1GB和2GB容量的microSD可能主宰新帝一半以上的獲利來源。

觀察目前microSD和一般SD卡的價差,就可知道高容量的microSD獲利空間有多大。以1GB容量的microSD為例,microSD零售價格約新台幣1,100元,幾乎是一般SD卡的2倍;而2GB容量價差更大,microSD的零售價格約3,000元,一般SD卡價格約1,000~1,300元,而目前台模組廠已加入供貨的512MB microSD,和一般SD卡價差就沒這麼高。

新帝第二季獲利成長36%,淨利達9,560萬美元,每股盈餘為0.47美元,據了解,貢獻新帝獲利最鉅的部份,除了固定的權利金收入外,就屬這些高容量的microSD,因為其獨佔市場以及身為價格、規格主導者的優勢,讓新帝享受的毛利率真的很驚人!

新帝和東芝(Toshiba)是因為身為SD規格主導者,加上SDA(SD card Association)不像MMCA(MultiMediaCard Association)是開放性的組織,因此在記憶卡規格的設計上,新帝和東芝握有絕對主導權,當初就是將microSD的規格訂成初期僅相容東芝晶片,三星電子(Samsung Electronics)、海力士(Hynix)等規格的晶片,都被排拒於外,因此得以享受產品推出初期的高溢價。

基於此原因,台模組廠在microSD推出的腳步上,往往落後新帝一大段時間,當新帝推512MB容量時,模組廠僅有256MB容量的microSD,而當新帝1GB、2GB問世時,模組廠512MB容量的microSD才隨後上市。

隨插卡式手機的需求興起,1GB的microSD告缺已有一段時間,台系模組廠雖然沒有自製能力,但多半四處在香港、大陸或美洲等地區,像貿易商購買未貼牌的microSD,然後再貼牌售出,主要是因為客戶需要,只好用此方式應急。

然新帝對於此狀況也相當感冒,因此對於通路商私下售予競爭對手microSD的方式,抓得相當嚴格,但在缺貨之際,台模組廠只有各憑本事,展開調貨能力。

台模組廠突圍! 高容量microSD市場大地震 新帝、金士頓難再憑藉東芝而獨大 台廠獲三星助陣跨向1GB舞台

(記者連于慧∕台北) 2006/09/13

由於三星電子(Samsung Electronics)63奈米NAND型快閃記憶體(Flash)近期陸續供貨,台系模組廠終於正式跨入1GB高容量microSD市場,包括威剛(3260)、創見(2451)、勁永(6145)均將於10月推出1GB microSD,打破擁有東芝(Toshiba)NAND型Flash晶片支援的新帝(SanDisk)、金士頓(Kingston)獨霸高容量microSD市場局面,預料市佔率爭奪戰亦將隨即引爆。

台模組廠表示,目前市場上1GB容量microSD貨源相當有限,供貨極為吃緊,有能力自製1GB microSD廠商僅有東芝陣營的新帝、金士頓,且是以2顆東芝4Gb MLC(Multi-Level Cell)晶片堆疊而成,由於三星等其他NAND型Flash大廠晶片均無法放入microSD,加上東芝貨源難以取得,使得台系模組廠在1GB microSD市場只得缺席,僅能透過買水貨方式來貼牌銷售,然供貨亦是段段續續。

不過,隨著三星63奈米4Gb MLC晶片即將於9月底、10月初陸續出貨,台廠1GB microSD可望如雨後春筍般相繼問世,目前各家模組廠包括威剛、創見、勁永等腳步相當一致,都計劃在10月推出1GB microSD,屆時將打破新帝、金士頓等大廠獨大局面,同時價格亦會隨著供給增加而逐漸向下修正。

台模組廠指出,在摩托羅拉(Motorola)、諾基亞(Nokia)等國際手機大廠強力支援下,目前microSD已是手機用小型記憶卡相當普遍規格,並已取代miniSD成為市場主流,另根據市調機構預估,2006年底插卡式手機佔整體手機出貨量將達4成,相較於2005年比重僅18~20%,成長速度驚人。

事實上,小型記憶卡在推出初期係以手機搭售為主,然隨著NAND型Flash價格下滑及第二片記憶卡需求出籠,促使零售市場需求逐漸興起,不過,台模組廠供貨產品最高容量只有512MB,至於1GB及2GB容量只有新帝等少數廠商供應,造成市場供給吃緊,儘管台廠終於打破1GB microSD市場獨大局面,然在更高容量2GB方面,台廠短期內仍難有突破,國際大廠仍將擁有絕對優勢。